# GDI: Power efficient and less transistor count technique for logic designs

### Neha Mishra, G.R.Mishra

*Abstract*— GDI, i.e., Gate Diffusion Input is the latest technology for the designing of VLSI circuits. Comparing it to other designing techniques such as CMOS and PTL, GDI is considered as more efficient technique. GDI technique consumes less power, less area and it also has lower complexity of designing. Performance of any circuit is based on its delay, power and the area, and GDI is the technique in which all the above three constraints are maintained with respect to other designing techniques. This paper gives the comparative study if GDI and other techniques with respect to area , power consumed ,delay and complexity of design. This paper also gives the advantages of GDI.

Index Terms-GDI, CMOS, PTL, complexity of design

#### I. INTRODUCTION

With the advance research in IC technology integration of more devices on a single chip is possible. This helps in reducing area. GDI is a technique which is suitable for design of fast, low power circuits using reduced number of transistors compared to traditional CMOS designs. PTL(pass-transistor logic) is also one of the logic that is popular in low power circuits. The basic disadvantage behind the PTL is at reduced power supply it gives slow operation and high input voltage level at the regenerative inverter is not  $V_{dd}$ , the PMOS device in the inverter is not fully turned off and hence direct path static power dissipation is significant[1]. So as compared to traditional CMOS design and existing PTL technique GDI technique is more suitable for fast and low power circuits using less transistors.

The aim of this paper is to compare the GDI technique with other traditional techniques and the give the difference in power dissipation and area.

Transistor count is a primary concern which largely affects the design complexity of larger circuit. For submicron CMOS technology area, topology selection, power dissipation and speed are very important aspect for high speed and low power application. These issues can be overcome by incorporating Gated Diffusion Input (GDI) technique[2].

The organization of the paper is as follows: Section 1 briefs the introduction, Section 2 describes the basic GDI cell and its design ,Section 3 gives the comparison of GDI technique with other techniques Section 4 presents the advantages of GDI, Section 5 gives simulation and results and lastly Section 6 gives Conclusion.

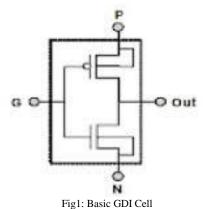

#### II. BASIC GDI CELL

The Gate diffusion Input is based on the use of a simple cell. At first look the basic GDI cell reminds of CMOS inverter but there is difference between two

- The GDI cell contains three inputs G(common gate input of NMOS and PMOS),P(input to the source/drain of PMOS), and N(input to the source/drain of PMOS)

- Bulks of both NMOS and PMOS are connected to Nor P(respectively), so it can be arbitrarily biased at contrast with a CMOS inverter[1].

rigi. Dasie ODi Celi

Here from the GDI cell a simple change in the input can lead to six different functions. These functions are very hard to implement in traditional designing techniques but s way more easier in GDI designing technique . Most of the methods are based in F1 and F2 functions.

Six different Boolean functions are:

- N=0, P=B, G=A OUT=ĀB (FUNCTION F1)

- N=B, P=1 ,G=A OUT=Ā+B (FUNCTION F2)

- N=1, P=B, G=A OUT=A+B (OR FUNCTION)

- N=B,P=0,,G=A OUT=AB (AND FUNCTION)

- N=0, P=1, G=A OUT=Ā (NOT FUNCTION)

# III. COMPARISON OF GDI WITH OTHER TECHNIQUES.

A. Power dissipation due to hazards and critical race conditions, leakage and direct path currents, power consuming transitions in unused circuitry and pre-charge transistors. A fast arithmetic operation requires fast circuit and the fast circuits require small size to minimize the delay effects of wires. Small size implies a single chip implementation, to minimize wire de- lays, and to make it possible to implement these fast circuits as part of a larger single chip system to minimize input/output delays [5].Performance

criteria for logic styles are circuit speed, circuit size, power

**Neha Mishra,** Department of Electronics and Communication Engineering, Amity School of Engineering & Technology, Amity University Uttar Pradesh, Lucknow Campus

**G.R.Mishra**, Department of Electronics and Communication Engineering, Amity School of Engineering & Technology, Amity University Uttar Pradesh, Lucknow Campus

dissipation, and wiring complexity as well as ease-of-use and generality of gates in cell-based design techniques[7].

GDI technique uses less complex designs hence results in less number of devices , less area, less delay, and less power dissipation.

TABLE II gives the design layout of the different logic techniques

|     | GDI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | CMOS                                 | TG            | N-FG          |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|---------------|---------------|

| 203 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                      |               |               |

|     | 4 transistors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 12 transitions                       | 5 transistors | 6 transistors |

| AND |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | x+€] ±+€] ↓<br>x+€] ±+€] ↓<br>x+€] ↓ |               | ÷             |

|     | 2 transistors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6 transistors                        | 6 transistors | 4 transistors |

| GR  | Reference of the second |                                      |               |               |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                      |               |               |

#### TABLE I

TABLE III gives the comparison of various designing

techniques with respect to transistor count ,delay and power consumption.

| FEATURES             | CSL          | CPL         | DPL          | GDI         |

|----------------------|--------------|-------------|--------------|-------------|

| TRANSISTORS<br>COUNT | HIGH         | LOW         | LOW          | VERY<br>LOW |

| DELAY                | HIGH         | VERY<br>LOW | VERY<br>HIGH | LOW         |

| POWER<br>CONSUMPTION | VERY<br>HIGH | LOW         | HIGH         | VERY<br>LOW |

#### TABLE III

## IV. ADVANTAGES OF GDI

The major advantage of GDI technique is less transistor count. As we can see that MUX design is a complex design which by CMOS logic requires 8-12 transistors and requires only 2 transistors in case of GDI design.

Table 4 gives the comparison of transistor count of static CMOS and GDI

| TABLE 4  |     |      |  |  |  |  |  |  |

|----------|-----|------|--|--|--|--|--|--|

| FUNCTION | GDI | CMOS |  |  |  |  |  |  |

| INVERTER | 2   | 2    |  |  |  |  |  |  |

| OR       | 2   | 6    |  |  |  |  |  |  |

| AND      | 2   | 6    |  |  |  |  |  |  |

| MUX      | 2   | 12   |  |  |  |  |  |  |

| XOR      | 4   | 16   |  |  |  |  |  |  |

| XNOR     | 4   | 16   |  |  |  |  |  |  |

| NAND     | 4   | 4    |  |  |  |  |  |  |

| NOR      | 4   | 4    |  |  |  |  |  |  |

#### V. SIMULATION RESULTS

Here in this section different gates are simulated using PSPICE. Gates are designed by both using CMOS and GDI, both are compared by their power dissipation A. AND GATE

| NC       | DE | VOLTAGE | NOI | )E | VOLTAGE   | NO | DE | VOLTAGE | NO | DE | VOLTAGE |

|----------|----|---------|-----|----|-----------|----|----|---------|----|----|---------|

|          | 1) | 0.0000  | (   | 2) | 5.0000    | (  | 3) | 4.9991  | (  | 4) | 0.0000  |

| 85<br>85 | 5) | 4.9991  | (   | 6) | 21.73E-12 |    |    |         |    |    |         |

|          |    |         |     |    |           |    |    |         |    |    |         |

TOTAL POWER DISSIPATION 2.50E-04 WATTS

Fig:2 Simulation results of AND gate using CMOS

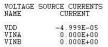

NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE

0.0000 2) 0.0000 ( 3) 1.4884 ( 4) 5.0000 1)

| VOLTAGE | SOURCE | CURRENTS |

|---------|--------|----------|

| MAME    | C1     | IDDENT   |

| VDD | -8.532E-12 |

|-----|------------|

| VA  | 0.000E+00  |

| VB  | 0.000E+00  |

|     |            |

TOTAL POWER DISSIPATION 4.27E-11 WATTS

Fig:3. Simulation results of AND gate using GDI technique

#### B. OR GATE

NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE

| ( | 1) | 0.0000 | ( | 2)   | 5.0000   | ( | 3) | 4.9991 | ( | 4) | 0.0000 |

|---|----|--------|---|------|----------|---|----|--------|---|----|--------|

| : | 5) | 4.9991 | ( | 6) 2 | 1.73E-12 |   |    |        |   |    |        |

VOLTAGE SOURCE CURRENTS NAME CURREN'

| VDD  | -4.999E-05 |

|------|------------|

| VINA | 0.000E+00  |

| VINB | 0.000E+00  |

TOTAL POWER DISSIPATION 2.50E-04 WATTS

Fig :4 Simulation result of OR gate using CMOS

NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE

1) 0.0000 ( 2) 0.0000 ( 3) 1.4884 ( 4) 5.0000

| VOLTAGE<br>NAME | SOURCE CURRENTS<br>CURRENT |

|-----------------|----------------------------|

| VDD             | -1.354E-11                 |

| VIN1            | 0.000E+00                  |

| VIN2            | 7.033E-12                  |

TOTAL POWER DISSIPATION 6.77E-11 WATTS

#### Fig 6:Simulation result of OR gate using GDI

#### C. XOR GATE

| NODI | Ξ  | VOLTAGE   | NC | DE  | VOLTAGE | NO | DE  | VOLTAGE   | NC | DE | VOLTAGE   |

|------|----|-----------|----|-----|---------|----|-----|-----------|----|----|-----------|

| C    | 1) | 0.0000    | (  | 2)  | 0.0000  | C  | 3)- | 486.6E-15 | (  | 4) | 86.89E-12 |

| (    | 5) | 43.45E-12 | (  | 6)  | 5.0000  | (  | 7)  | 5.0000    | (  | 8) | 5.0000    |

| C    | 9) | 5.0000    | (  | 10) | 5.0000  |    |     |           |    |    |           |

| VOLTAGE<br>NAME | SOURCE CURRENTS<br>CURRENT |

|-----------------|----------------------------|

| VDD             | -2.004E-11                 |

| VA              | 0.000E+00                  |

| VB              | 0.000E+00                  |

|                 |                            |

TOTAL POWER DISSIPATION 1.00E-10 WATTS

Fig:7 Simulation result of XOR gate using CMOS

#### International Journal of Engineering and Applied Sciences (IJEAS) ISSN: 2394-3661, Volume-4, Issue-5, May 2017 (Approved by University Grants Commission, India)

| NC | DE              | VOLTAGE    | NODE                                | VOLTAGE   | NODE    | VOLTAGE  | NO | DE | VOLTAGE |

|----|-----------------|------------|-------------------------------------|-----------|---------|----------|----|----|---------|

| (  | 1)              | 0.0000     | (2)                                 | 5.0000    | ( 3     | ) 5.0000 | C  | 4) | 0.0000  |

| (  | 5)              | 1.4884     |                                     |           |         |          |    |    |         |

|    | VOL             | TAGE SOURC | F CURRENT                           | ·5        |         |          |    |    |         |

|    | NAM             |            | CURRENT                             | 0         |         |          |    |    |         |

|    | VDD<br>VA<br>VB | ÷          | 1.855E-11<br>7.033E-12<br>0.000E+00 |           |         |          |    |    |         |

| 2  | TOT             | AL POWER I | ISSIPATIO                           | N 9.28E-1 | 1 WATTS | 9        |    |    |         |

\*\*\*\* 05/29/13 14:32:20 \*\*\*\*\*\*\* PSpice 10.5.0 (Jan 2005) \*\*\*\*\*\*\* ID# 0 \*\*\*\*\*\*\*\* GDI XOR

Fig: 8 Simulation result of XOR gate using GDI

Table 5 shows the comparison of power dissipation of CMOS and GDI technique with respect to different gates.

TABLE 5

| GATES/CIRCUIT | CMOS     | GDI      |

|---------------|----------|----------|

| NOT           | 2.51E-11 | 2.51E-11 |

| AND           | 2.50E-04 | 4.27E-11 |

| OR            | 2.50E-04 | 6.77E-11 |

| XOR           | 1.00E-10 | 9.28E-11 |

#### VI. CONCLUSION

In this paper GDI technique was presented. The GDI technique allows use of a simple and efficient design algorithm, based on the Shannon expansion[1]. Here in this by the result of simulation we can say that power dissipation is less in the GDI technique compared to CMOS technique. Here we have also seen that transistor count is less in GDI technique compared to other techniques. So in today's digital era use of GDI technique is much more efficient than other techniques.

#### ACKNOWLEDGEMENT

The authors are thankful to Hon'able C – VI, Dr. AseemChauhan (Additional President, RBEF and Chancellor AUR, Jaipur), Maj. General K. K. Ohri (AVSM, Retd.) Pro-VC Amity University, Uttar Pradesh Lucknow, Wg. Cdr. Dr. Anil Kumar, Retd.(Director, ASET), Prof. S. T. H. Abidi (Professor Emeritus), Brig. U. K. Chopra, Retd.(Director AIIT), for their motivation, kind cooperation, and suggestions.

#### REFERENCES

- M. Pedram, S. Nazarian, "Thermal Modeling, Analysis, and Management in VLSI Circuits: Principles and Methods", Proceedings of the IEEE, Vol. 94, No. 8, pp. 1487-1501, 2006

- [2] E. S. Fetzer, M. Gibson, A. Klein, N. Calick, Z. Chengyu, E. Busta, and B. Mohammad, "A fully bypassed six-issue integer datapath and register file on the Itanium-2 microprocessor," IEEE J. Solid-State Circuits, vol. 37, no. 11, pp. 1433–1430, Nov. 2002.

- [3] S. Naffziger, B. Stackhouse, T. Grutkowski, D. Josephson, J. Desai, E.Alon, and M. Horowitz, "The implementation of a 2-core multithreaded itanium family processor," IEEE J. Solid-State Circuits, vol.41, no. 1, pp. 197–209, Jan. 2006.

- [4] A. Morgenshtein, A. Fish, I.A. Wagner, "Gate-Diffusion Input (GDI)– A Power Efficient Method for Digital Combinational Circuits," IEEE Trans. VLSI, vol.10, no.5 pp.566-581, October 2002.IJSER © 2014 <u>http://www.ijser.org</u>\_International Journal of Scientific & Engineering Research, Volume 5, Issue 4, April-2014 862 ISSN 2229-5518

- [5] M. Golden, S. Arekapudi, G. Dabney, M. Haertel, S. Hale, L. Her-linger, Y. Kim, K. McGrath, V. Palisetti, and M. Singh, "A 2.6 GHz dualcore 64b x 86 microprocessor with DDR2 memory support," in IEEE ISSCC Dig. Tech. Papers, Feb. 2006, pp. 104–105.

- [6] A. M. Shams, T. K. Darwish and M. A. Bayoumi. "Permormance Analysis of Low Power 1-Bit CMOS full adder cells", IEEE Transaction on VLSI Systems, Vol. 10, Feb. 2002.

- [7] A. P. Chandrakasan, S. Sheng, and R. W. Brodersen, "Low-power CMOS digital design," IEEE J. Solid-State Circuits, vol. 27, pp. 473–484, Apr. 1992.

- [8] R. Zimmermann and W. Fichtner, "Low-power logic styles: CMOS versus pass-transistor logic," IEEE J. Solid-State Circuits, vol. 32, pp.1079–1090, June 1997.

- [9] K. Yano, Y. Sasaki, K. Rikino, and K. Seki., "Top-down pass- transistor logic design," IEEE J. Solid-State Circuits, vol. 31, no. 6, pp. 792-803, Jun. 1996.

- [10] M. Anis, M. Allam, and M. Elmasry, "Impact of technology scaling on CMOS logic styles," IEEE Trans. Circuits and Systems II: Analog and Digital Signal Processing, vol. 49, no. 8, pp. 577-588, Aug. 2002.

- [11] G. Merrett and B. M. Al-Hashimi, "Leakage power analysis and comparison of deep submicron logic gates," in Proc. 14th Int.Workshop on Power, Timing, Modeling, Optimization, and Simu- lation (PATMOS),pp. 198-207, Sep. 2004.

- [12] Bellaouar, A., and Elmasry, M. I., Low-Power Digital VLSI Design, Kluwer, Norwell, MA, 1995.

- [13] D. Radhakrishanan, S.R. Whitaker, G.K. Maki, Formal [14] L. Bisdounis, D. Gouvetas and O. Koufopavlou, "A comparative study of CMOS circuit design styles for low power high-speed VLSI circuits", Int. J. of Electronics, Vol. 84, (6): 599-613, 1998.

- [15] Sun, S., and Tsui, P., "Limitation of CMOS supply-voltage scaling by MOSFET threshold voltage", IEEE Journal of Solid-State Circuits, vol. 30, pp. 947-949, 1995.

- [16] D. Radhakrishanan, Low-voltage low-power CMOS full adder, in Proc. IEE Circuits Devices Syst., vol. 148, Feb. 2001.

- [17] Issam S. Abu-Khatter, Abdellatif bellaouar, and M.I. Elmasry, Circuit Techniques for CMOS Low-Power High-Performance Multipliers, IEEE J. Solid- State Circuits, 31(10): 1535-1546,1996.

Neha Mishra , was born in Gorakhpur (U.P.) India in 1991. She received her bachelor's degree of Engineering and Technology from BBDNIIT (U.P.) India in 2013. She has joined BBD University Lucknow U.P , as a lecturer in August 2013 to Aug 2015. She is currently working towards her M.Tech Degree in Electronics and Communication at Amity University, Lucknow. She is currently focused on her work on Gate Diffusion Input(GDI) Technique.

**G. R. Mishra**, obtained his Ph. D. in Electronics from Avadh University. He has over fourteen years experience and presently working as faculty members in Department of Electronics & Communication Engineering, Amity School of Engineering & Technology, Amity University Uttar Pradesh Lucknow Campus. He is life member of Institution of Electronics & Telecommunication Engineers (IETE), the Institution of Engineering & Technology (IET-UK) and Material Research Society of India (MRSI). He has presented several papers in National Seminar/Conferences and also published papers in National/international Journals. His area of interest includes Digital System Design, Microprocessor Based System Design, Signal Processing, Embedded Systems and VLSI Design.